中国北京--(BUSINESS WIRE)--(美国商业资讯)—作为业界领先的芯片和半导体IP供应商,致力于使数据传输更快更安全,Rambus Inc.(纳斯达克股票代码:RMBS)今日宣布,推出由PHY和控制器IP组成的PCI Express®(PCIe®)6.0接口子系统。Rambus PCIe Express 6.0 PHY还支持最新版本(3.0版本)的Compute Express Link™(CXL™)规范。

Rambus接口IP总经理Scott Houghton表示:“人工智能/机器学习(AI/ML)和数据密集型工作负载的快速发展正在推动数据中心架构的持续演进,并要求更高的性能水平。Rambus PCIe 6.0接口子系统可通过一流的延迟、功耗、面积和安全性,支持下一代数据中心对性能的要求。”

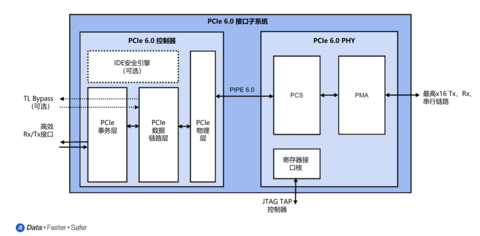

Rambus PCIe 6.0接口子系统的数据传输速率高达64GT/s,并且经过全面优化,可满足先进异构计算架构的需求。该子系统中的PCIe控制器具备完整性和数据加密(IDE)引擎,专门用于保护PCIe链接和通过它们传输的重要数据。另外在PHY方面,它还提供对CXL 3.0的全面PHY支持,支持缓存一致性内存共享、扩展和池化的芯片级解决方案。

IDC计算半导体研究副总裁Shane Rau表示:“PCIe在数据中心无处不在。为了支持新一代应用的更高性能要求,企业正在不断提升速度和带宽,进而使CXL的重要性日益提升。越来越多的芯片公司开始支持新的数据中心架构,因此获得高性能接口IP解决方案将成为实现该生态系统的关键。”

Rambus PCIe 6.0接口子系统有以下主要特性:

- 支持PCIe 6.0规范,包括64 GT/s数据传输速率和PAM4调制信号

- 实现低延迟前向纠错(FEC),保证链路稳健性

- 支持固定尺寸的FLIT,可实现高带宽效率

- 向后兼容PCIe 5.0、4.0和3.0/3.1

- 通过IDE引擎(控制器)实现最先进的安全性

- 支持CXL 3.0,用于优化内存资源的新使用模式(PHY)

更多信息:

如需了解更多PCIe 6.0接口子系统有关信息,敬请访问:rambus.com/interface-ip/serdes/pcie6-phy/。

关注Rambus:

公司网址: rambus.com

Rambus博客: rambus.com/blog

Twitter: @rambusinc

LinkedIn: www.linkedin.com/company/rambus

Facebook: www.facebook.com/RambusInc

WeChat ID: Rambus_China

关于Rambus

Rambus是一家业界领先的芯片和半导体IP提供商, 致力于使数据传输更快、更安全。凭借30多年先进的半导体研发经验,作为高性能内存子系统研发先驱,解决了数据密集型系统所面临的内存与数据处理之间的瓶颈。无论是云端,边缘,或手中的互联设备,这些实时且沉浸式的应用均依赖于数据的吞吐率和完整性。Rambus的产品和创新提供了更大的带宽和容量以及更高的安全性,以满足全球的数据需求并驱动着前所未有的用户体验。更多相关信息,请访问rambus.com网站。