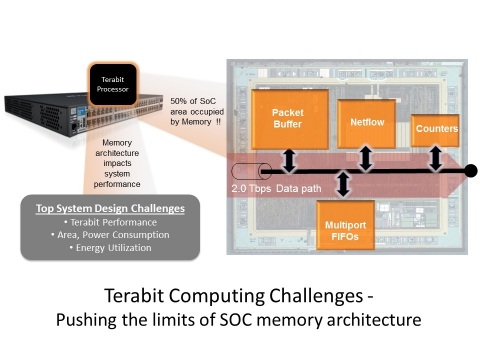

SANTA CLARA, Calif.--(BUSINESS WIRE)--Memoir Systems Inc., today announced the immediate availability of Renaissance for Datacom, a new family of multiport memory generators that enables SoC architects to push the performance envelope of their next generation multi-terabit networking products. Developers of datacom SoCs can rapidly create ultra-high performance memory solutions for fundamental functional blocks including packet buffers, Netflow, policing and state tables, statistics counters, and multi-port FIFOs. Renaissance for Datacom is the first product to incorporate the company’s new pattern-aware technology that generates memory IPs with dramatically better performance, and lower area and power. Renaissance for Datacom addresses the needs of customers building terabit networking hardware for next generation datacenters, high performance switches and routers, software defined networks (SDN) and cloud infrastructure.

“There are fundamental limitations with existing silicon technology that need to be overcome to enable terabit networking. As we crank up switching bandwidths into the terabit domain, the power consumption and heat generation alone make these solutions problematic for large scale data centers,” said Martin Izzard, former R&D VP at TI who is now CEO at a stealth mode startup. “Terabit era networks will require new innovative technologies such as Memoir’s Renaissance for Datacom that not only enable higher bandwidths, but also are much more energy-efficient.”

With its new pattern-aware technology, Renaissance for Datacom provides ultra-high performance multiport memories that were previously infeasible. Renaissance for Datacom is built on top of Memoir’s Renaissance 2X, 4X, and 10X families of embedded memories (based on Memoir’s award-winning Algorithmic Memory®), which offer deterministic, fully random access memory performance up to 10X memory operations per second (MOPS). Although many applications require deterministic memory performance, some only access memory in a specific pattern. Renaissance for Datacom recognizes four common memory patterns: allocation access used in packet buffers, read modify write access used to update memory in Netflow, policing and state tables, read add modify access used to maintain statistics counters, and sequential access used in multi-port FIFOs. The product includes four unique memory cores – Allocation, Update, Counter and Sequential memory core tailored for the above functions. These represent patterns that are commonly used, independent of the implementation, in a wide set of applications in the datacom SoCs.

Pattern-aware technology enables Renaissance for Datacom to extend memory performance all the way up to 16X MOPS for datacom SoCs. For instance, using an 8R8W allocation memory, developers can build a fully deterministic shared memory buffer with multi-terabit bandwidth in 28 nm process. Another key benefit of pattern-aware technology is its ability to reduce area, power and energy consumption. With a typical high performance SoC burning 80-100W, lowering the power and energy envelope is critical. Pattern-aware technology reflects a deeper understanding of the memory access patterns that in turn enables more intelligent management of memory. It enables fine grained power control of physical memory and reduces memory energy consumption by up to 70%, translating to up to 5% lower energy consumption on end systems.

“Renaissance for Datacom memories are extremely scalable,” said Sundar Iyer, Memoir’s CEO and co-founder. “Our customers can now deliver deterministic performance of several terabits of network bandwidth. Moreover, the memories are generic by design in that they don’t make any assumptions about specific implementations.”

Renaissance for Datacom offers fully deterministic memory performance, activity aware power control, and runtime error detection and correction. It offers physical design aware RTL and that is exhaustively formally verified, with no further silicon verification required. The memories use simple SRAM like interfaces, and integrate into a normal SoC design flow. Since the memories are RTL based, they are compatible with any process, node, or foundry. For more information, contact sales@memoir-systems.com.

About Memoir Systems, Inc.

Memoir Systems, Inc. is a provider of breakthrough memory technology that is delivered as Semiconductor Intellectual Property (SIP). Memoir’s revolutionary approach to memory design shortens the time required to develop new memories, and can increase the performance of existing memory macros by up to 10X more Memory Operations Per Second (MOPS). The company’s Renaissance family of products provides drop-in replacements for existing embedded memories. These new memories offer increased performance or reduced area and power consumption without sacrificing performance. Memoir’s technology is optimized for a particular process, node, and foundry and integrates seamlessly into any existing SoC design flow. Since the introduction of the company in October of 2011, Memoir Systems has received several industry accolades and awards including: winning a DesignVision award at DesignCon in February 2012; named to EE Times “Silicon 60” list of emerging start-ups in April 2012 and named as A Red Herring Top 100 North America Tech Startup in May 2012. Memoir Systems is based in Santa Clara, California and has additional research and development facilities located in Hyderabad, India and Yerevan, Armenia. For more information, visit www.memoir-systems.com.

Memoir, Algorithmic Memory, Synthesized Memory, Renaissance, and the Memoir Systems logo are trademarks or registered trademarks of Memoir Systems Inc. in the United States and other countries. Memoir Systems and other parties may also have trademark rights in other terms used herein.

The URL for this release is located at: www.memoir-systems.com